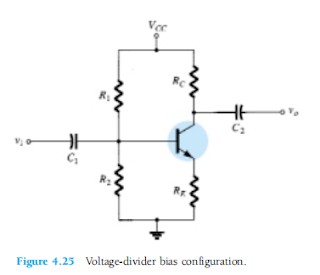

Sub Bab 7.4 Voltage Divider Biasing

1. Tujuan[Kembali]

- Mengetahui apa itu Voltage Divider Biasing

- Mengetahui rangkaian dari Voltage Divider Biasing

- Dapat mensimulasikan rangkaian Voltage Divider Biasing

- Alat

Instrumen

Alat ukur untuk mengukur Kuat Arus dalam satuan Ampere

- Osiloskop

- Bahan

- Kapasitor

Kapasitor adalah komponen elektronik pasif yang dapat menyimpan muatan listrik dalam waktu sementara dengan satuan kapasitansinya adalah Farad.

- Resistor

Resistor adalah komponen Elektronika Pasif yang memiliki nilai resistansi atau hambatan tertentu yang berfungsi untuk membatasi dan mengatur arus listrik dalam suatu rangkaian Elektronika

- Ground

Pentanahan merupakan titik acuan yang biasa digunakan sebagai acuan titik potensial nol atau titik tegangan nol pada rangkaian elektronika. Fungsi ground meliputi:

Titik Referensi Tegangan: Ground berfungsi sebagai titik referensi umum yang digunakan dalam sirkuit elektronik. Ketika sinyal atau voltase diukur dalam suatu rangkaian, mereka diukur relatif terhadap titik pentanahan. Ini memungkinkan untuk menjaga konsistensi dan menghindari potensi mengambang yang dapat menyebabkan masalah di sirkuit.

Pengalihan Arus: Ground berfungsi sebagai jalur untuk pengalihan arus kembali ke sumber listrik atau sumber ground, terutama untuk rangkaian DC. Ketika arus mengalir melalui komponen, seperti resistor atau transistor, mereka mengalir dari sumber tegangan melalui jalur ground kembali ke sumber listrik.

Mengurangi Kebisingan dan Interferensi: Ground digunakan sebagai jalur untuk mengalirkan gangguan atau kebisingan yang mungkin muncul di sirkuit elektronik. Dengan menemukan jalur tanah yang tepat dan merancang jalur tanah yang bersih, kebisingan dan interferensi dapat diminimalkan, sehingga meningkatkan kinerja dan keandalan sistem elektronik.

- Transistor FET

Pengaturan bias pembagi tegangan yang diterapkan pada amplifier transistor BJT juga diterapkan pada amplifier FET seperti yang ditunjukkan oleh Gambar. 6.20.

Konstruksi dasarnya benar-benar sama, tetapi analisis DC masing-masing sangat berbeda. Ig 0 A untuk FET amplifiers, tetapi besarnya Ib untuk penguat BJT umum-emitor dapat mempengaruhi DC tingkat arus dan tegangan di sirkuit input dan output. Ingat bahwa Ib menyediakan hubungan antara sirkuit input dan output untuk konfigurasi pembagi tegangan BJT sementara Vgs akan melakukan hal yang sama untuk konfigurasi FET.

Gambar 6. 20 halaman 264

Gambar 4.25 halaman 158

Tegangan VG, sama dengan tegangan pada R2, dapat ditemukan menggunakan aturan pembagi tegangan sebagai berikut:

Dengan menggunakan hukum KVL (gambar 6.21) didapatkan persamaan :

Hasilnya menentukan bahwa setiap kali kita merencanakan Persamaan. (6.16), jika kita memilih ID 0 mA, the nilai VGS untuk plot adalah VG volts. Titik yang baru saja ditentukan muncul pada Gambar. 6.22.

Persamaan (6.16). Perpotongan garis lurus dengan kurva transfer di wilayah tersebut di sebelah kiri sumbu vertikal akan menentukan titik operasi dan yang sesuai level ID dan VGS. Karena persimpangan pada sumbu vertikal ditentukan oleh ID VG / RS dan VG adalahdiperbaiki oleh jaringan input, meningkatkan nilai RS akan mengurangi tingkat ID di terseksi seperti yang ditunjukkan pada Gambar. 6.23. Cukup jelas dari Gambar 6.23 bahwa:

Peningkatan nilai RS menghasilkan nilai ID diam yang lebih rendah dan nilai VGS yang lebih negatif.

Setelah nilai diam IDQ dan VGSQ ditentukan, jaringan yang tersisa analisis dapat dilakukan dengan cara biasa. Itu adalah,

1. Tentukan pada jaringan dalam gambar 7.85

a. VG

b. IDQ dan VGSQ

c. VD dan VS

d. VDSQ

Jawab :

2. Tentukan pada jaringan dalam gambar 7.86

a. ID

b. VS dan VDS

c. VG dan VGS

d. VP

Jawab :

3.

- Tentukan IDQ dan VGSQ dari rangkaian berikut ini

Jawab : Untuk karakteristik transfer, jika ID = IDSS>4 = 8 mA>4 = 2 mA, maka VGS =

VP>2 = -4 V>2 = -2 V. Kurva yang dihasilkan mewakili persamaan Shockley

muncul di Gambar 7.22. Persamaan jaringan didefinisikan oleh

Garis bias yang dihasilkan muncul pada Fig. 7.22 dengan nilai diam

IDQ= 2.4 mA dan VGSQ = -1.8 V

2. Tentukan VD dan VS dari rangkaian berikut ini

1. Manakah dari hubungan berikut yang benar tentang arus gerbang?

a. SG=ID+IS

b. ID=IG

c. IS= IG

d. IG=0

e. ID=0

Jawab: d. Struktur fisik FET yang mengandung silikon dioksida memberikan ketahanan tak terbatas. Oleh karena itu tidak ada arus yang akan mengalir melalui terminal gerbang.

2. Apa yang akan terjadi jika nilai Rs tambah?

a. VGs Meningkat

b. VGs Mengurang

c. VGs =Rs

d. VGs Tetap sama

e. VGs=0

Jawab: b. Meningkatnya nilai Rs menghasilkan nilai quiescent yang lebih rendah dari ID dan lebih banyak nilai negatif dari VGs.

3. Apa arus yang mengalir melalui R1 resistor untuk pembagi tegangan (R1=R2=1KΩ, VDD=10V)?

a. 2mAb. 5mA

c. 3mA

d. 1mA

e. 2mA

Jawab: b. IR1=IR2 =VDD/(R1+R2 )

IR1 = 10/2KΩ

IR1 = 5mA.

Semua kapasitor, termasuk kapasitor bypass C S , telah diganti dengan "sirkuit terbuka"

setara. Selain itu, sumber V DD dipisahkan menjadi dua sumber yang setara untuk memungkinkan pemisahan lebih lanjut dari daerah masukan dan keluaran jaringan. Karena IG = 0 A, hukum Kirchhoff saat ini mengharuskan IR1 = IR2, dan deret rangkaian ekuivalen yang muncul di sebelah kiri gambar dapat digunakan untuk mencari level V G . Itu tegangan V G , sama dengan tegangan pada R2,

- Video

Video 7.17

Video 7.21

- File Proteus 7.17 : Klik Disini

- File Proteus 7.18 : Klik Disini

- File Proteus 7.21 : Klik Disini

- Video Pembahasan Proteus 7.17 : Klik Disini

- Video Pembahasan Proteus 7.18 : Klik Disini

- Video Pembahasan Proteus 7.21 : Klik Disini

- Datasheet resistor : disini

- Datasheet voltmeter : disini

- Datasheet transistor : disini

- Datasheet kapasitor : disini

- Datasheet osiloskop : disini